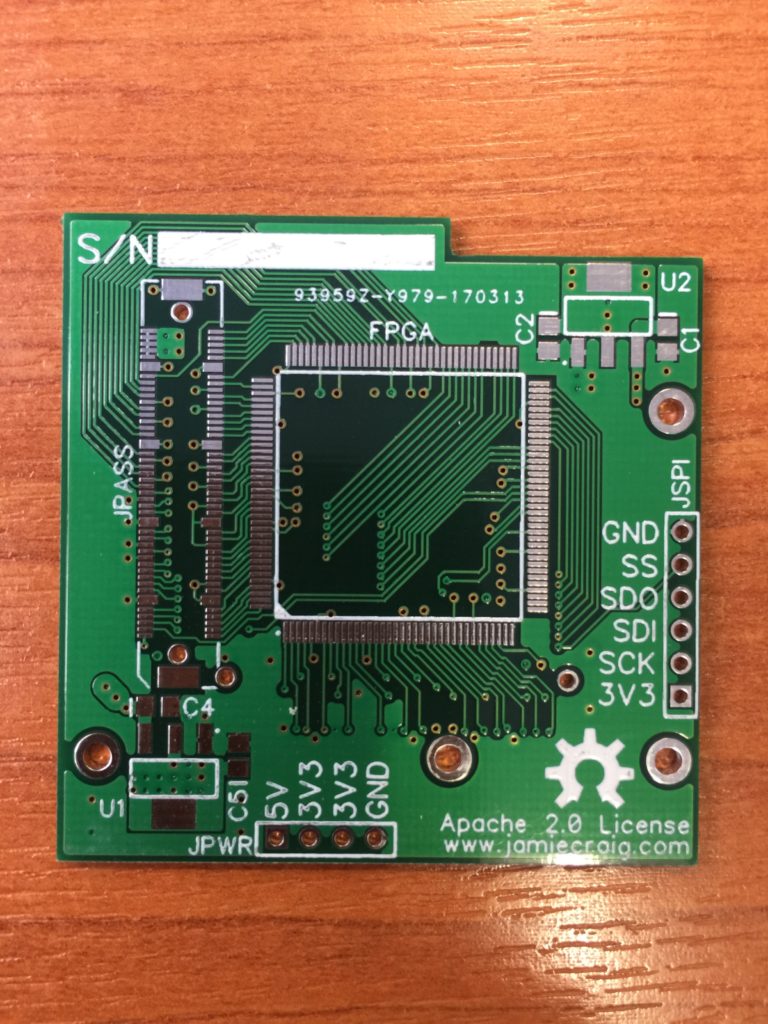

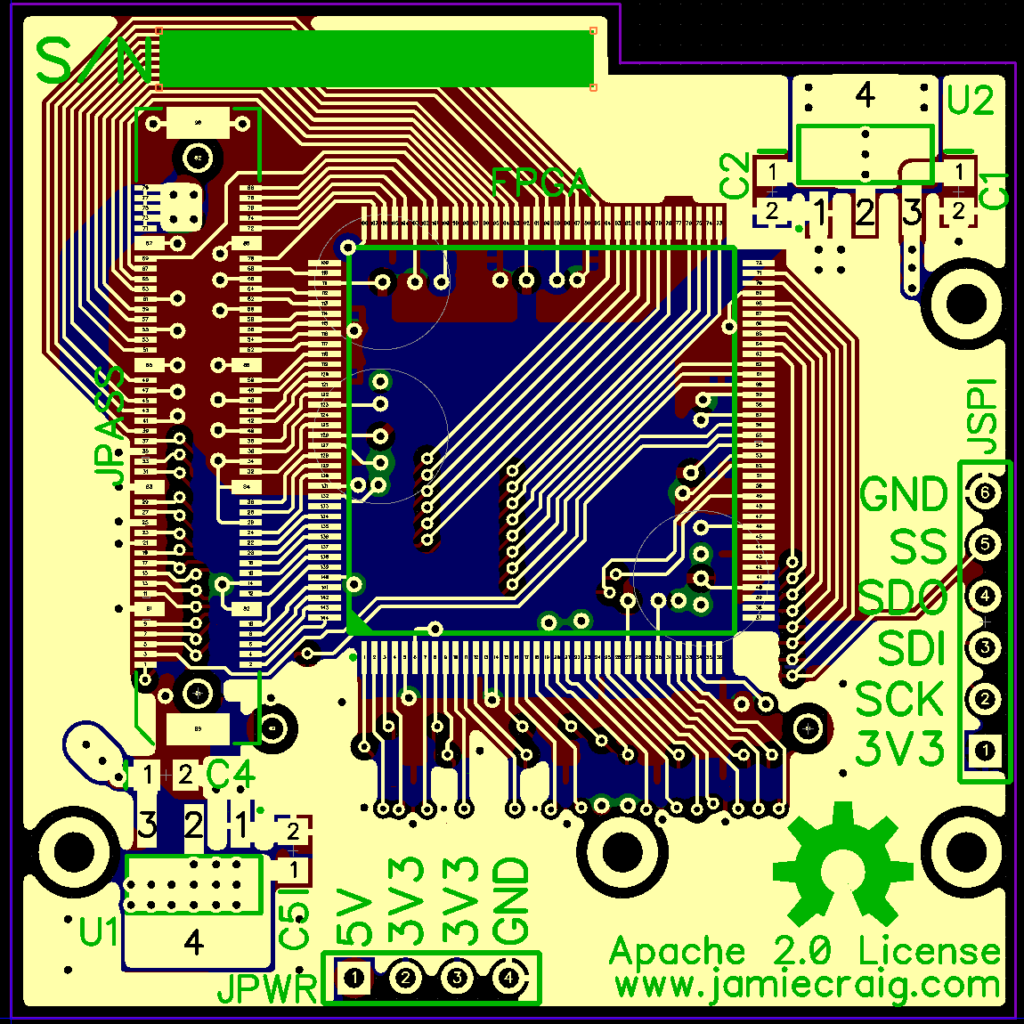

I’ve now got the iCE40 add-on board for the novena up and running. There are a couple of defects on the board design that need corrected before you can get one of these boards to run. These are:

Missing power to the VCC_SPI pin (pin 72, top pin on the right-hand side of the chip, nearest the 1.2V regulator) – this just needs jumpered to any available 3.3V point. Since it’s the very corner pin, there’s no difficulty connecting this by hand.

Bad footprint for the pass-through connector – the FX10A_80P_8 connector footprint I’ve used is too narrow, and it makes it very difficult to solder by hand. Reflow should be OK as long as the solder resist layer isn’t excessively thick on your boards – the pads are in the right place, just too short.

I’ll do a revision of the board layout when I get some time, but for now, this is pretty functional.

I’ve written a basic loader for the iCE40 , which uses a slightly modified GPBB Xilinx bitstream for now. I hope to write a proper bus bridge for the Xilinx to interface between the two ICs, but for now it’s enough to get blinkenlights working. The sources (and a copy of the compiled Xilinx bitstream) are available here.

I’ve also included a basic blinkenlights demo for the GPBB when piggy-backed on the iCE40.

Also about this board: